System-on-Chip Design Data Flow hardware Implementation

> Hao Zheng Dept. Comp Sci & Eng U of South Florida <u>haozheng@usf.edu</u> (813) 9744757

### **Single-Rate SDF to Hardware**

Single-rate SDF: all production/consumption rates are a fixed number = 1.

-The entire circuit controlled by a single clock.

- Implementation

- –Actors -> combination circuits

- -Queues -> wires

- –Initial tokens -> registers.

#### **Single-Rate SDF to Hardware**

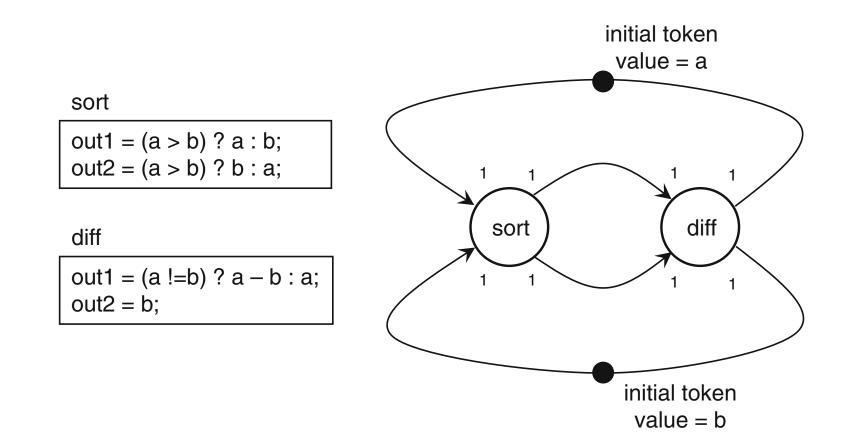

Fig. 3.10 Euclid's greatest common divisor as an SDF graph

#### **Single-Rate SDF to Hardware**

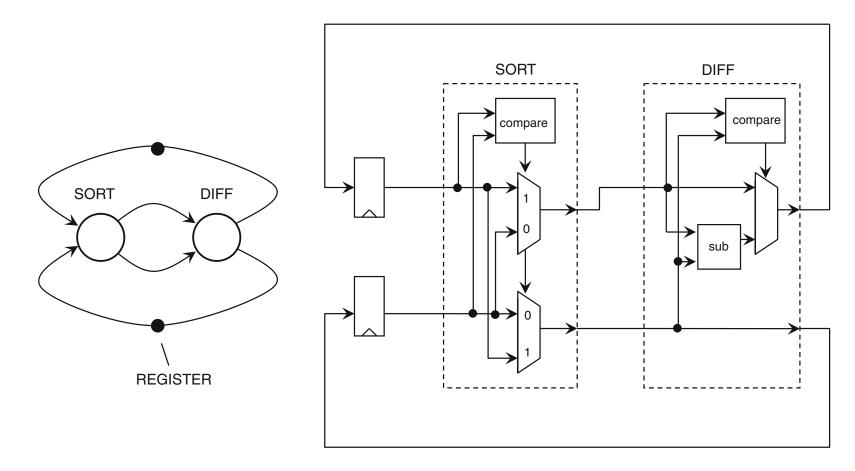

Fig. 3.11 Hardware implementation of euclid's algorithm

Can lead to long combination paths.

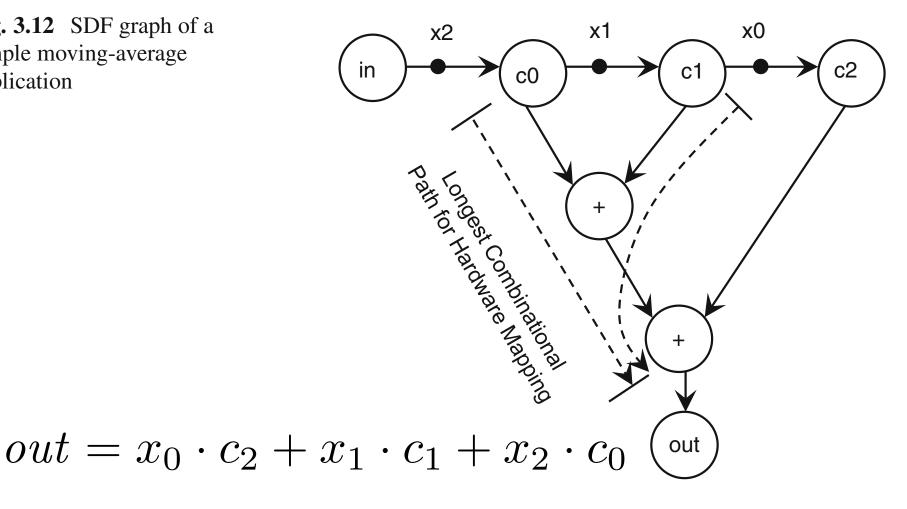

### **SDF HW Implementation**

- Combinational path is a sequence of actors s.t. edges between these actors do not have initial token.

- Critical path is a combinational path s.t. the sum of latencies of all actors on that path is the longest.

- Critical path delay determines the clock frequency.

- -Should be minimized to increase clock speed.

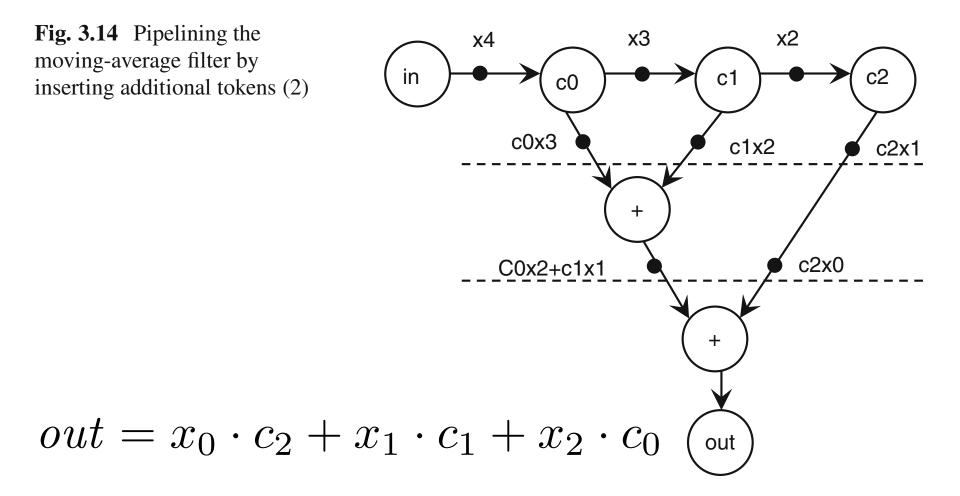

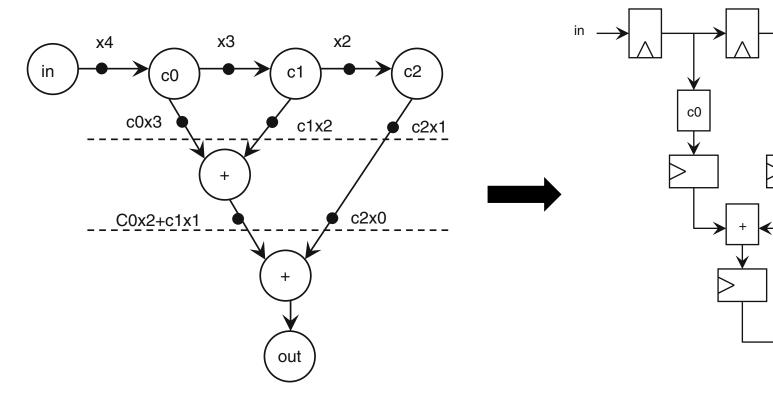

Fig. 3.12 SDF graph of a simple moving-average application

c2

c1

out

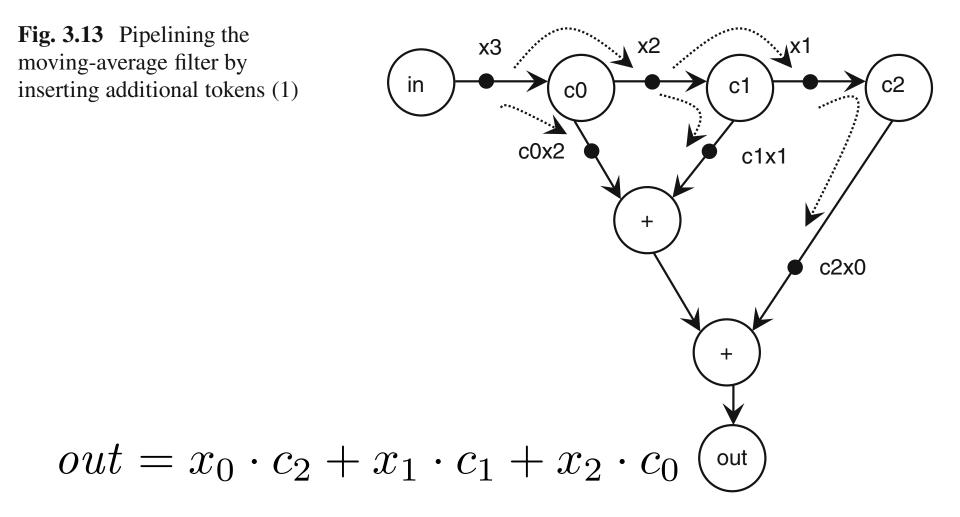

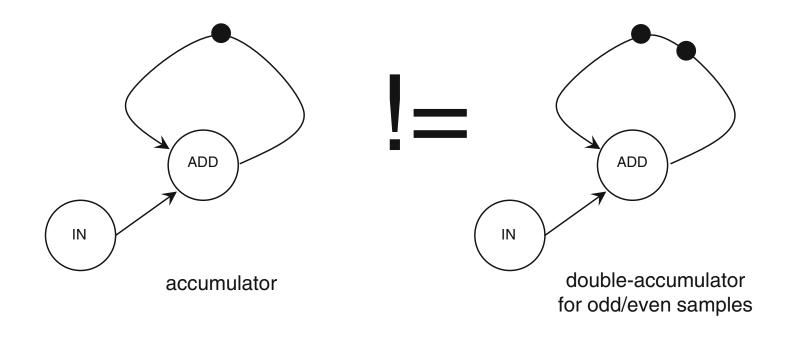

# **Pipelining: Pitfall**

Do Not add initial tokens unless they can be injected by a sequence of actor firings.

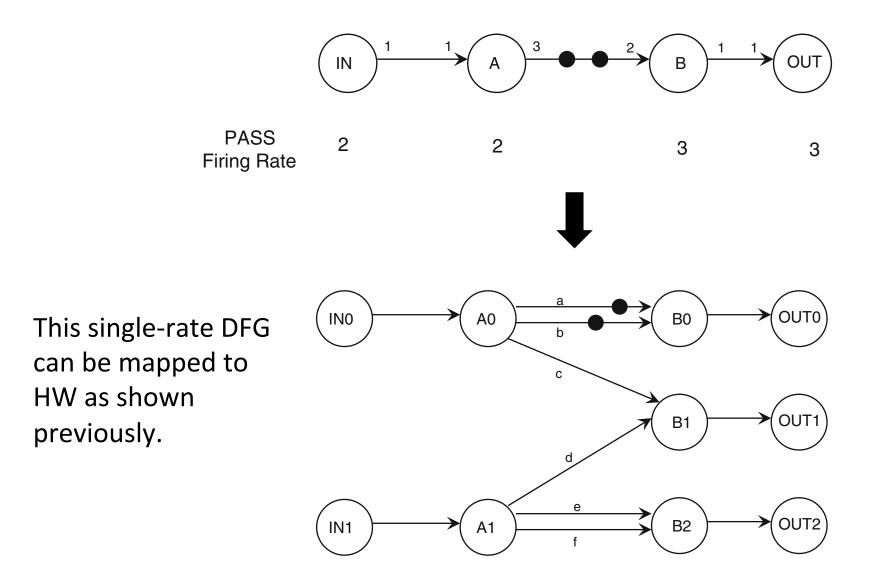

#### Multi-Rate Expansion (Sec. 2.5.1)

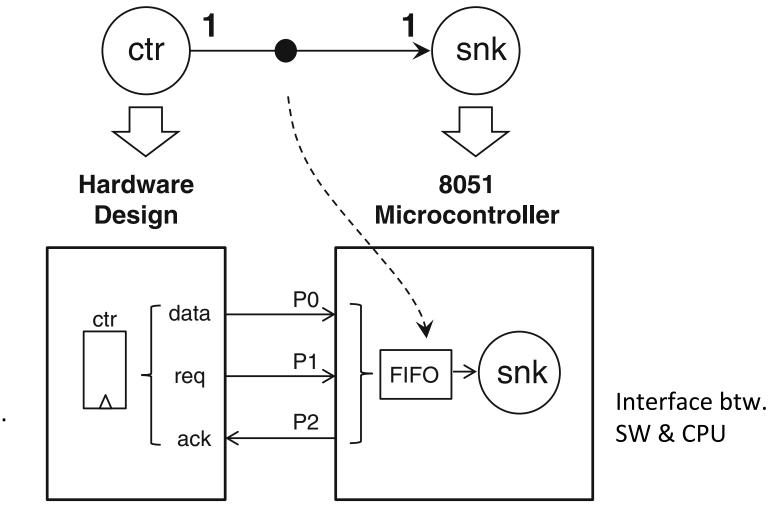

## **HW/SW Hybrid Implementation**

Interface btw. HW & CPU

## **Reading Guide**

• Section 3.2 - 3.3, the *CoDesign* book.