## CDA 4253/CIS 6930 FPGA System Design Modeling of Combinational Circuits

## Hao Zheng Dept of Comp Sci & Eng USF

## Reading

# → P. Chu, FPGA Prototyping by VHDL Examples → Chapter 3, RT-level combinational circuit → Sections 3.1 - 3.2, 3.5 - 3.7.

#### →XST User Guide for Virtex-6, Spartan-6, and 7 Series Devices

→ Chapter 3 and 7

## **VHDL Model Template: Recap**

library ieee; use ieee.std\_logic\_1164.all;

ARCHITECTURE architecture\_name OF entity\_name IS Signal & component declarations BEGIN

Concurrent statements

END [ARCHITECTURE] architecture\_name;

## **Concurrent Statements**

→ Simple concurrent signal assignment

- → z <= a **xor** b

- →Conditional signal assignment (when-else)

→selected concurrent signal assignment (with-select-when)

- → Process statements

- →To be covered later

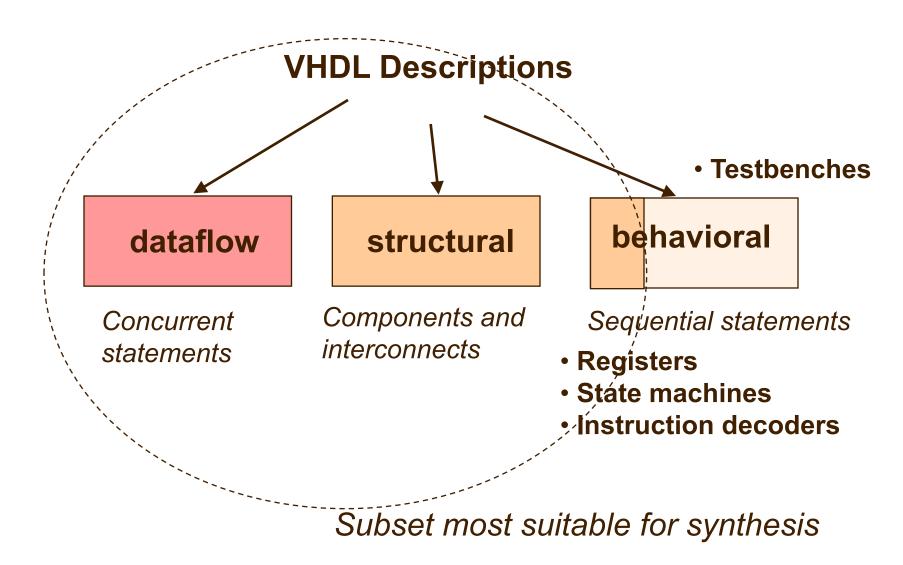

## **VHDL Modeling Styles**

## **Combinational Circuit Building Blocks**

## **Fixed Shifters & Rotators**

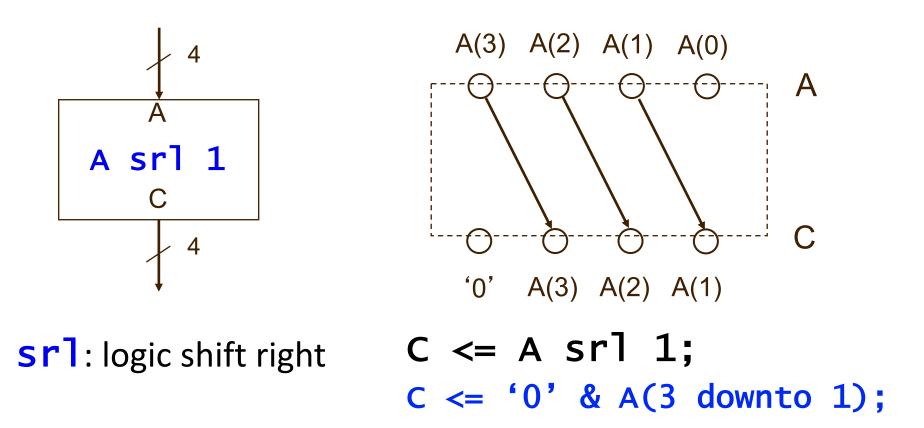

## **Fixed Logical Shift Right in VHDL**

SIGNAL A : STD\_LOGIC\_VECTOR(3 DOWNTO 0); SIGNAL C : STD\_LOGIC\_VECTOR(3 DOWNTO 0);

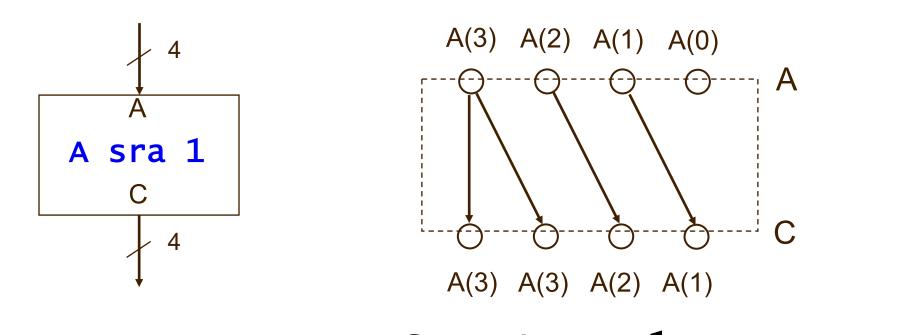

## **Fixed Arithmetic Shift Right in VHDL**

SIGNAL A : STD\_LOGIC\_VECTOR(3 DOWNTO 0); SIGNAL C : STD\_LOGIC\_VECTOR(3 DOWNTO 0);

**sra**: arithmetic shift left

C <= A sra 1; c <= A(3) & A(3 downto 1);</pre>

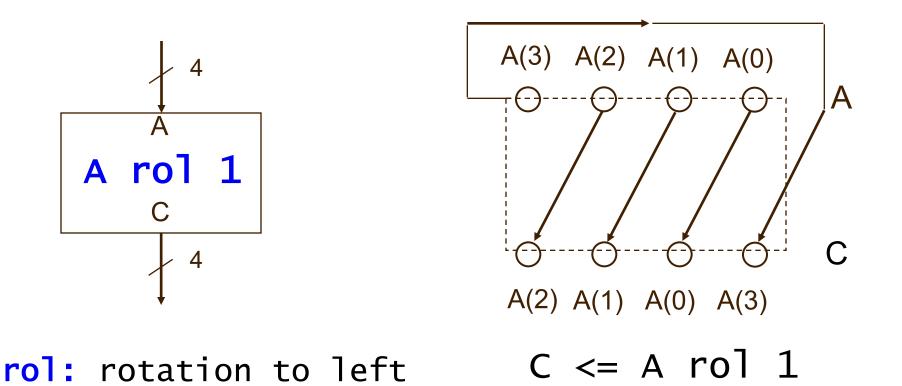

## **Fixed Rotation in VHDL**

SIGNAL A : STD\_LOGIC\_VECTOR(3 DOWNTO 0); SIGNAL C : STD\_LOGIC\_VECTOR(3 DOWNTO 0);

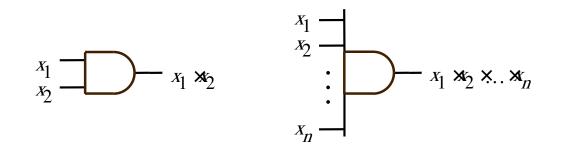

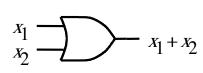

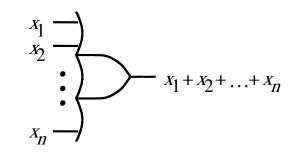

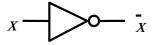

## **Logic Gates**

#### **Basic Gates – AND, OR, NOT**

(a) AND gates

(b) OR gates

(c) NOT gate

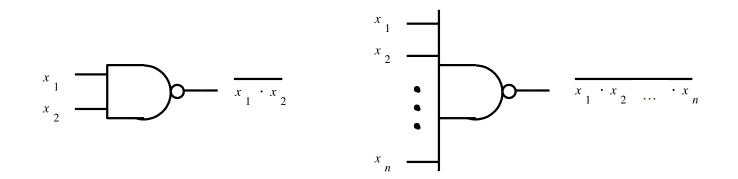

#### **Basic Gates – NAND, NOR**

(a) NAND gates

(b) NOR gates

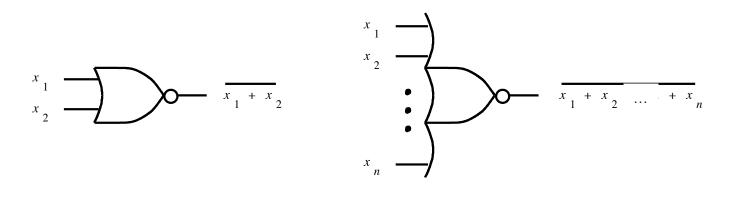

**Basic Gates – XOR**

| <i>x</i> <sub>1</sub> | <i>x</i> <sub>2</sub> | $f = x_1 \oplus x_2$ |                                                                                                                                                                          |

|-----------------------|-----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                     | 0                     | 0                    |                                                                                                                                                                          |

| 0                     | 1                     | 1                    |                                                                                                                                                                          |

| 1                     | 0                     | 1                    | $\begin{array}{c} x_1 \\ x_2 \end{array} \qquad $ |

| 1                     | 1                     | 0                    |                                                                                                                                                                          |

(a) Truth table

(b) Graphical symbol

(c) Sum-of-products implementation

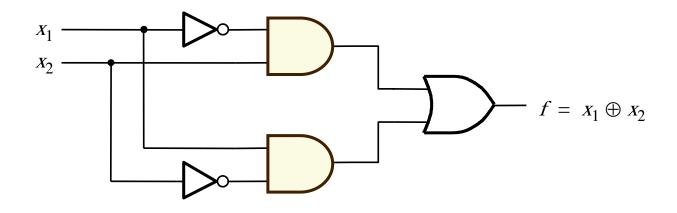

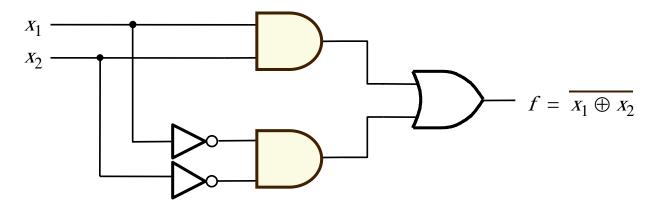

#### **Basic Gates – XNOR**

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$  | <i>x</i> <sub>1</sub> | <i>x</i> <sub>2</sub> | $x_2 \qquad f = \overline{x_1} \oplus$ | $\overline{X_2}$                                                                                                                                                         |

|-------------------------------------------------------|-----------------------|-----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | 0                     | 0                     | 0 1                                    |                                                                                                                                                                          |

|                                                       | 0                     | 1                     | 1 0                                    |                                                                                                                                                                          |

| 1 0 0 $f = \overline{X_1 \oplus X_2} = X_1 \odot X_2$ | 1                     | 0                     | 0 0                                    | $\begin{array}{c} x_1 \\ x_2 \end{array} \qquad $ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 1                     | 1                     | 1 1                                    |                                                                                                                                                                          |

(a) Truth table

(b) Graphical symbol

(c) Sum-of-products implementation

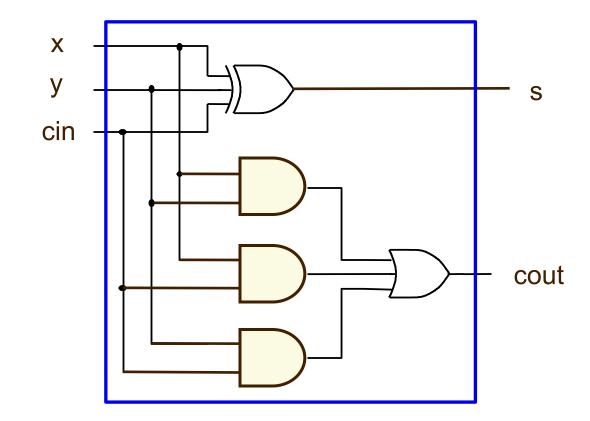

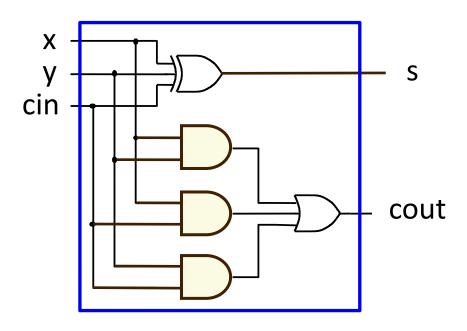

## **1-Bit Full Adder**

## **1-Bit Full Adder**

```

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

```

#### ENTITY falb IS

- PORT( x : IN STD\_LOGIC ;

- y : IN STD\_LOGIC ;

- cin : IN STD\_LOGIC ;

- s : OUT STD\_LOGIC ;

- cout : OUT STD\_LOGIC ) ;

END fa1b;

## **1-Bit Full Adder**

ARCHITECTURE dataflow OF falb IS BEGIN

END dataflow ;

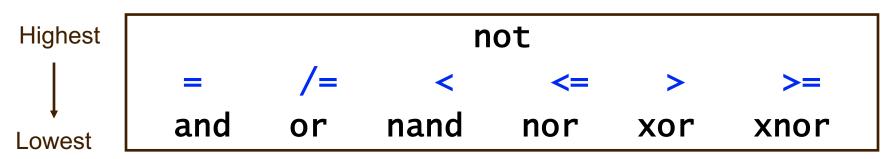

## **Logic Operators**

Logic operators

| and or nand nor xor not xnor |  |

|------------------------------|--|

|------------------------------|--|

## • Logic operators precedence

|        |     |    | 1    | not |     |      |

|--------|-----|----|------|-----|-----|------|

| Ļ      | and | or | nand | nor | xor | xnor |

| Lowest |     |    |      |     |     |      |

## **No Implied Precedence**

Wanted: y = ab + cd

#### Incorrect

$$y = (ab + c)d$$

#### Correct

# Modeling Routing Structures with Conditional Concurrent Signal Assignment (when-else)

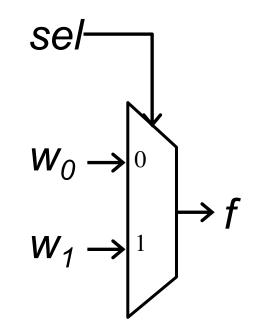

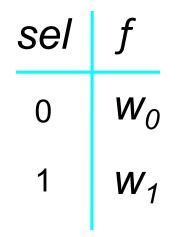

## 2-to-1 Multiplexer

#### (a) Graphical symbol

(b) Truth table

## 2-to-1 Multiplexer

```

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

```

ARCHITECTURE dataflow OF mux2to1 IS BEGIN

f <= w0 WHEN sel = '0' ELSE

w1;

END dataflow ;</pre>

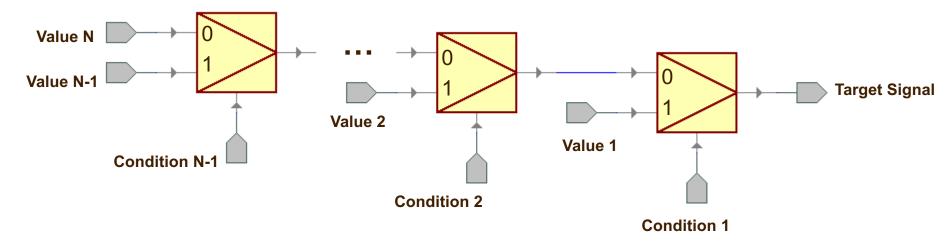

## **Conditional Concurrent Signal Assignment**

target\_signal <= value1 when condition1 else

value2 when condition2 else

...

value<sub>N+1</sub> when condition<sub>N+1</sub> else

value<sub>N</sub>;

- →Branches are evaluated one by one from top to bottom.

- →Induces priority among branches

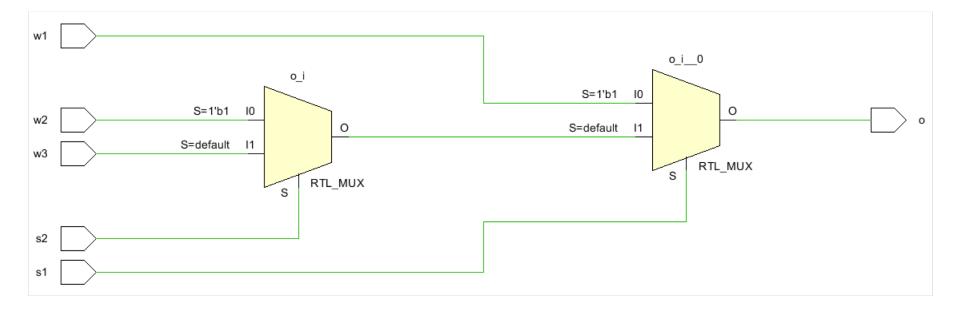

## **Cascade of Multiplexers**

LIBRARY ieee ;

USE ieee.std\_logic\_1164.all ;

ENTITY mux\_cascade IS

PORT (w1, w2, w3 : IN STD\_LOGIC ;

s1, s2 : IN STD\_LOGIC ;

f : OUT STD\_LOGIC );

END mux\_cascade ;

ARCHITECTURE dataflow OF mux\_cascade IS BEGIN

```

f <= w1 WHEN s1 = '1' ELSE

w2 WHEN s2 = '1' ELSE

w3;

END dataflow ;</pre>

```

## **Cascade of Multiplexers**

Notice the priority of selection.

## **Conditional Concurrent Signal Assignment**

target\_signal <= value1 when condition1 else

value2 when condition2 else

...

value<sub>N+1</sub> when condition<sub>N+1</sub> else

value<sub>N</sub>;

## **More Operators**

Relational operators

Logic and relational operators precedence

## Precedence of Logic and Relational Operators

- Comparison a = bc

- Incorrect

- $\dots$  when a = b and c else  $\dots$

- equivalent to

- ... when (a = b) and c else ...

#### Correct

... when a = (b and c) else ...

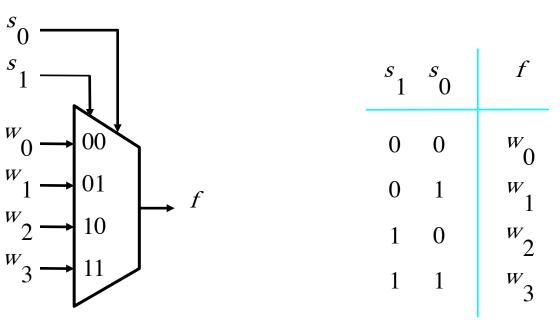

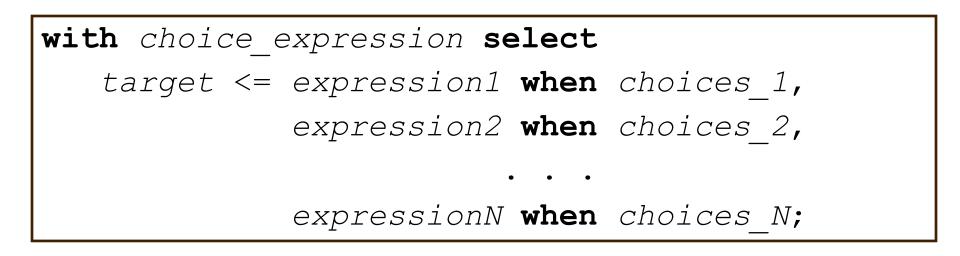

# Modeling Routing Structures with Selected Concurrent Signal Assignment (with-select-when)

## **4-to-1 Multiplexer**

(a) Graphic symbol

(b) Truth table

f

<sup>W</sup>0

No priority, and choices are disjoint.

## A 4-to-1 Multiplexer

```

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY mux4to1 IS

PORT( w0, w1, w2, w3 : IN STD_LOGIC ;

: IN STD_LOGIC_VECTOR(1 DOWNTO 0):

S

: OUT STD_LOGIC ) ;

END mux4to1 :

ARCHITECTURE dataflow OF mux4to1 IS

BEGIN

WITH S SELECT

```

```

f <= w0 WHEN "00", default condition

w1 WHEN "01",

w2 WHEN "10",

w3 WHEN OTHERS;

END dataflow;</pre>

```

## **Selected Concurrent Signal Assignment**

> All choices are mutually exclusive and cover all values of choice\_expression.

## **Selected Concurrent Signal Assignment**

## **Formats of Choices**

• when Expr

- when  $Expr_1 \mid \dots \mid Expr_N$

- this branch is taken if any of *Expr\_x* matches choice\_expression

when others

#### **Formats of Choices - Example**

##

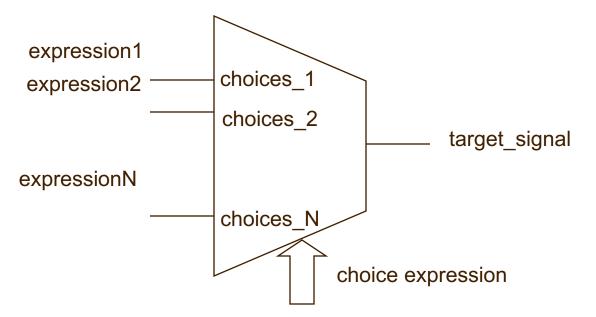

## **Decoders**

#### **2-to-4 Decoder**

| En | w<br>1 | w<br>0 | У3 | <sup>y</sup> 2 | <i>y</i> <sub>1</sub> | <i>y</i> <sub>0</sub> |

|----|--------|--------|----|----------------|-----------------------|-----------------------|

| 1  | 0      | 0      | 0  | 0              | 0<br>1<br>0<br>0      | 1                     |

| 1  | 0      | 1      | 0  | 0              | 1                     | 0                     |

| 1  | 1      | 0      | 0  | 1              | 0                     | 0                     |

| 1  | 1      | 1      | 1  | 0              | 0                     | 0                     |

| 0  | X      | X      | 0  | 0              | 0                     | 0                     |

|    |        |        |    |                |                       |                       |

(a) Truth table

(b) Graphical symbol

## VHDL Code for a 2-to-4 Decoder

```

-- ITBRARY not shown

ENTITY dec2to4 IS

PORT ( w : IN STD_LOGIC_VECTOR(1 DOWNTO 0) ;

En : IN STD_LOGIC ;

y : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );

END dec2to4 ;

ARCHITECTURE dataflow OF dec2to4 IS

SIGNAL Enw : STD_LOGIC_VECTOR(2 DOWNTO 0) ;

BEGIN

Enw <= En & w ;

WITH Enw SELECT

y <= "0001" WHEN "100",

"0010" WHEN "101",

"0100" WHEN "110",

"1000" WHEN "111",

"0000" WHEN OTHERS ;

```

END dataflow ;

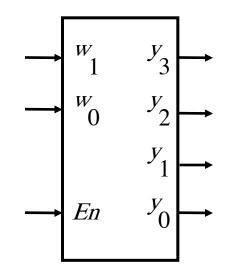

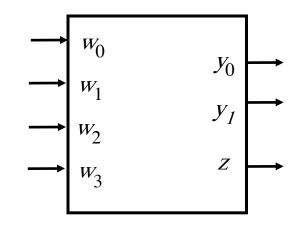

# **Encoders**

# **Priority Encoder**

| W <sub>3</sub> | <i>W</i> <sub>2</sub> | <i>w</i> <sub>1</sub> | W <sub>0</sub> | <i>Y</i> <sub>1</sub> | <i>Y</i> <sub>0</sub> | Z |

|----------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|---|

| 0              | 0                     | 0                     | 0              | Х                     | X                     | 0 |

| 0              | 0                     | 0                     | 1              | 0                     | 0                     | 1 |

| 0              | 0                     | 1                     | X              | 0                     | 1                     | 1 |

| 0              | 1                     | X                     | X              | 1                     | 0                     | 1 |

| 1              | X                     | X                     | X              | 1                     | 1                     | 1 |

# **VHDL code for a Priority Encoder**

```

-- library not shown

ENTITY priority IS

PORT ( w : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y : OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

z : OUT STD_LOGIC );

END priority ;

```

ARCHITECTURE dataflow OF priority IS BEGIN

y <= "11" when w(3) = '1' else "10" when w(2) = '1' else "01" when w(1) = '1' else "00" when others;

z <= '0' when w = "0000" else '1' when others; END dataflow ;

# **Adders**

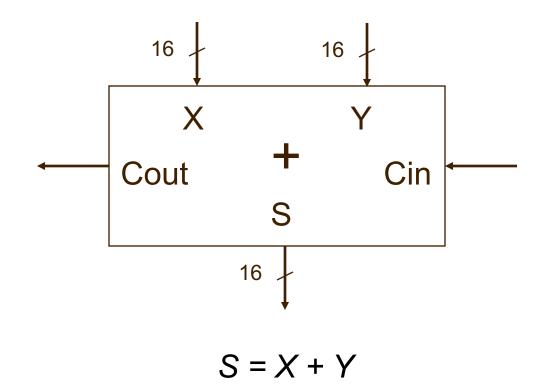

#### **16-bit Unsigned Adder**

# **Operations on Unsigned Numbers**

For operations on **unsigned** numbers

```

USE

ieee.numeric std.all

and

signals of the type UNSIGNED

and

conversion functions std logic vector(), unsigned()

OR USE

ieee.std logic unsigned.all

and

signals of the type STD_LOGIC VECTOR

```

#### **16-bit Unsigned Adder**

```

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

USE ieee.std_logic_unsigned.all;--non-IEEE standard

```

| ENTITY adder16 IS |       |                                            |

|-------------------|-------|--------------------------------------------|

| <b>PORT</b> ( Cin | : IN  | STD_LOGIC ;                                |

| Х                 | : IN  | <pre>STD_LOGIC_VECTOR(15 DOWNTO 0) ;</pre> |

| Y                 | : IN  | <pre>STD_LOGIC_VECTOR(15 DOWNTO 0) ;</pre> |

| S                 | : OUT | <pre>STD_LOGIC_VECTOR(15 DOWNTO 0) ;</pre> |

| Cout              | : OUT | <pre>STD_LOGIC ) ;</pre>                   |

| END adder16 :     |       |                                            |

ARCHITECTURE dataflow OF adder16 IS

SIGNAL Sum : STD\_LOGIC\_VECTOR(16 DOWNTO 0) ;

BEGIN

```

Sum <= ('0' & X) + Y + Cin ;

S <= Sum(15 DOWNTO 0) ;

Cout <= Sum(16) ;

END dataflow ;</pre>

```

# **Addition of Unsigned Numbers (1)**

LIBRARY ieee ; USE ieee.std\_logic\_1164.all ; **USE ieee.numeric\_std.all;** -- IEEE standard

ENTITY adder16 IS PORT( Cin X Y S Cout END adder16 ;

- : IN STD\_LOGIC ;

- : IN STD\_LOGIC\_VECTOR(15 DOWNTO 0);

- : IN STD\_LOGIC\_VECTOR(15 DOWNTO 0);

- : OUT STD\_LOGIC\_VECTOR(15 DOWNTO 0);

- : OUT STD\_LOGIC );

## **Addition of Unsigned Numbers (2)**

ARCHITECTURE dataflow OF adder16 IS **SIGNAL** Xu, Yu : UNSIGNED(15 DOWNTO 0); **SIGNAL** Su : UNSIGNED(16 DOWNTO 0); BEGIN Xu <= unsigned(X);</pre> Yu <= unsigned(Y);  $Su \ll ('0' \& Xu) + Yu + unsigned('0' \& Cin)$ • S <= std\_logic\_vector(Su(15 DOWNTO 0)) ;</pre> Cout <= Su(16) ; **END** dataflow :

**Signed** and **unsigned** are arrays of std\_logic.

### **Operations on Signed Numbers**

For operations on signed numbers

• Either use

ieee.numeric\_std.all, signals of the type SIGNED, and conversion std\_logic\_vector(), signed()

• Or use

ieee.std\_logic\_signed.all, and

signal type STD\_LOGIC\_VECTOR

### Signed/Unsigned Types in numeric\_std

→ Behave exactly like

#### std\_logic\_vector

- → They determine whether a given vector should be treated as a signed or unsigned number.

- → Prefer to use

ieee.numeric\_std.all;

- → Use either numeric\_std or std\_logic\_unsigned (or signed).

- $\rightarrow$  Do NOT mix them together.

# **Multipliers**

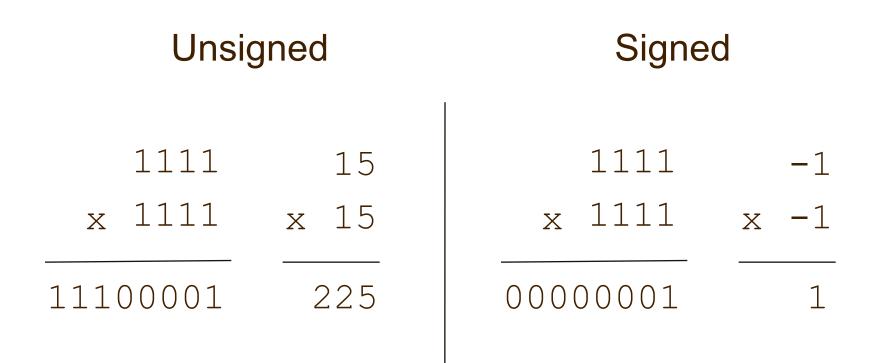

# **Unsigned vs. Signed Multiplication**

In Xilinx, a multiplier can be implemented either in a DSP or CLB

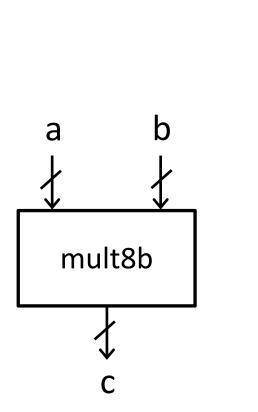

### **8x8-bit Unsigned Multiplier**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

entity mult8b is

port(...);

end mult8b;

architecture arch of mult8b is

begin

c <= a * b;

end arch;

```

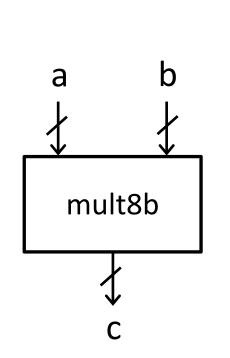

#### **8x8-bit Signed Multiplier**

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

entity mult8b is

port(...);

end mult8b;

architecture arch of mult8b is

begin

c <= a * b;

end arch;

```

## **Signed/Unsigned Multiplication**

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all ;

entity multiply is

port(

a : in STD_LOGIC_VECTOR(7 downto 0);

b : in STD_LOGIC_VECTOR(7 downto 0);

cu : out STD_LOGIC_VECTOR(15 downto 0);

cs : out STD_LOGIC_VECTOR(15 downto 0));

end multiply;

architecture dataflow of multiply is

begin

-- signed multiplication

cs <= std_logic_vector(signed(a)*signed(b));</pre>

-- unsigned multiplication

CU <=

std_logic_vector(unsigned(a)*unsigned(b));

end dataflow;

```

### **Multiplication with Constants**

→ If either A or B in A \* B is a constant, more efficient implementation with shifts and additions.

#### *A* \* 9

# can be implemented as $A \le 3 + A$

#### **Operators in <u>numeric\_std</u>** Package

| overloaded<br>operator                                 | description             | data type<br>of operand a                                  | data type<br>of operand b                                  | data type<br>of result                   |

|--------------------------------------------------------|-------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|

| abs a<br>- a                                           | absolute value negation | signed                                                     |                                                            | signed                                   |

| a * b<br>a / b<br>a mod b<br>a rem b<br>a + b<br>a - b | arithmetic<br>operation | unsigned<br>unsigned, natural<br>signed<br>signed, integer | unsigned, natural<br>unsigned<br>signed, integer<br>signed | unsigned<br>unsigned<br>signed<br>signed |

| a = b<br>a /= b<br>a < b<br>a <= b<br>a > b<br>a >= b  | relational<br>operation | unsigned<br>unsigned, natural<br>signed<br>signed, integer | unsigned, natural<br>unsigned<br>signed, integer<br>signed | boolean<br>boolean<br>boolean<br>boolean |

#### **Parameterized Models**

#### **Design Reuse**

→ How to design for the 32-bit problem below?

$$O = A + B + C$$

→Create a new 32-bit adder

→waste of effort

# →Reuse previously designed adder →but it is 16-bit

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity gen_add_w_carry is

generic(N : integer := 4);

port(

a, b : in std_logic_vector(N - 1 downto 0);

cout : out std_logic;

sum : out std_logic_vector(N - 1 downto 0)

);

end gen_add_w_carry;

architecture arch of gen_add_w_carry is

signal a_ext, b_ext, sum_ext : unsigned(N downto 0);

begin

a_ext <= unsigned('0' & a);</pre>

b_ext <= unsigned('0' & b);</pre>

sum_ext <= a_ext + b_ext;</pre>

sum <= std_logic_vector(sum_ext(N - 1 downto 0));</pre>

cout <= sum_ext(N);</pre>

end arch

```

#### **Instances of Generic Models**

-- instantiate 8-bit adder adder\_8\_unit: work.gen\_add\_w\_carry(arch) generic map(N = > 8) port map(a = > a8, b = > b8, cout = > c8, sum = > sum 8)); -- instantiate 16-bit adder adder\_16\_unit: work.gen\_add\_w\_carry(arch) generic map(N = > 16) port map(a = >a16, b = >b16, cout=>c16, sum=>sum16)); -- instantiate 4-bit adder -- (generic mapping omitted, default value 4 used) adder\_4\_unit: work.gen\_add\_w\_carry(arch) port map(a > a4, b > b4, cout > c4, sum > sum4);

## **A Word on Generics**

→ Generics are typically **integer** values

- In this class, the entity inputs and outputs should be std\_logic or std\_logic\_vector.

- → But the generics should be integer.

- → Generics are given a default value

→ GENERIC ( N : INTEGER := 16 ) ;

- This value can be overwritten when entity is instantiated as a component

- → Generics are very useful when instantiating an often-used component

- → Need a 32-bit register in one place, and 16-bit register in another

- Can use the same generic code, just configure them differently

#### **Constants – Make Code More Readable**

Syntax:

#### **constant** name : type := value;

#### **Examples:**

constant init\_val : STD\_LOGIC\_VECTOR(3 downto 0) := "0100"; constant ANDA\_EXT : STD\_LOGIC\_VECTOR(7 downto 0) := X"B4"; constant counter\_width : INTEGER := 16; constant buffer\_address : INTEGER := x"FFFE"; constant clk\_period : TIME := 20 ns; constant strobe\_period : TIME := 333.333 ms;

#### **Constants vs Generics**

→Constants:

- →Create symbolic names

- Make code more readable

- → Declared in packages, entity, or architecture.

- →Cannot create generic designs: still need two design entities for Adder\_8b and Adder\_32b.

→Generics:

- Can be passed through design hierarchy through component instantiation

- →Used for creating generic designs: a single design entity Adder for Adder\_8b and Adder\_32b.

#### **Binary to BCD Conversion**

for(i=0; i<8; i++) { // add 3 to a column if it is >= 5for each column if (column >= 5) column += 3;// shift binary digits left 1 Hundred << 1; Hundreds[0] = Tens[3];Tens << 1; Tens[0] = Ones[3];Ones << 1; Ones[0] = Binary[7];Binary << 1;

}

- 1. If the binary value in any of the BCD columns is 5 or greater, add 3 to that value in that BCD column.

- 2. Shift the binary number left one bit.

- 3. If 8 shifts have taken place, the BCD number is in the *Hundreds*, *Tens*, and *Ones* column. Terminate

- 4. Otherwise, go to 1.

#### Example:

| Hundreds | Tens | Ones | Binary   |

|----------|------|------|----------|

| 0000     | 0000 | 0000 | 11110011 |

| 100's | 10's | 1's  | Binary   | Operation |

|-------|------|------|----------|-----------|

| 0000  | 0000 | 0000 | 10100010 |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

| 100's | 10's | 1's  | Binary   | Operation |

|-------|------|------|----------|-----------|

| 0000  | 0000 | 0000 | 10100010 |           |

| 0000  | 0000 | 0001 | 0100010  | << 1      |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

| 100's | 10's | 1's  | Binary   | Operation |

|-------|------|------|----------|-----------|

| 0000  | 0000 | 0000 | 10100010 |           |

| 0000  | 0000 | 0001 | 0100010  | << 1      |

| 0000  | 0000 | 0010 | 100010   | << 1      |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

| 100's | 10's | 1's  | Binary   | Operation |

|-------|------|------|----------|-----------|

| 0000  | 0000 | 0000 | 10100010 |           |

| 0000  | 0000 | 0001 | 0100010  | << 1      |

| 0000  | 0000 | 0010 | 100010   | << 1      |

| 0000  | 0000 | 0101 | 00010    | << 1      |

| 0000  | 0000 | 1000 | 00010    | +3        |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

|       |      |      |          |           |

| 100's | 10's | 1's  | Binary   | Operation |

|-------|------|------|----------|-----------|

| 0000  | 0000 | 0000 | 10100010 |           |

| 0000  | 0000 | 0001 | 0100010  | << 1      |

| 0000  | 0000 | 0010 | 100010   | << 1      |

| 0000  | 0000 | 0101 | 00010    | << 1      |

| 0000  | 0000 | 1000 | 00010    | +3        |

| 0000  | 0001 | 0000 | 0010     | << 1      |

| 0000  | 0010 | 0000 | 010      | << 1      |

| 0000  | 0100 | 0000 | 10       | << 1      |

|       |      |      |          |           |

|       |      |      |          |           |

#### Shift and Add-3 (Double-Dabble)

| 100's | 10's | 1's  | Binary   | Operation |

|-------|------|------|----------|-----------|

| 0000  | 0000 | 0000 | 10100010 |           |

| 0000  | 0000 | 0001 | 0100010  | << 1      |

| 0000  | 0000 | 0010 | 100010   | << 1      |

| 0000  | 0000 | 0101 | 00010    | << 1      |

| 0000  | 0000 | 1000 | 00010    | +3        |

| 0000  | 0001 | 0000 | 0010     | << 1      |

| 0000  | 0010 | 0000 | 010      | << 1      |

| 0000  | 0100 | 0000 | 10       | << 1      |

| 0000  | 1000 | 0001 | 0        | << 1      |

| 0000  | 1011 | 0001 | 0        | +3        |

#### Shift and Add-3 (Double-Dabble)

| 100's | 10's   | 1's  | Binary    | Operation |      |

|-------|--------|------|-----------|-----------|------|

|       |        |      | 1010 0010 |           | -162 |

|       |        | 1    | 010 0010  | << #1     |      |

|       |        | 10   | 10 0010   | << #2     |      |

|       |        | 101  | 0 0010    | << #3     |      |

|       |        | 1000 |           | add 3     |      |

|       | 1      | 0000 | 0010      | << #4     |      |

|       | 10     | 0000 | 010       | << #5     |      |

|       | 100    | 0000 | 10        | << #6     |      |

|       | 1000   | 0001 | 0         | << #7     |      |

|       | 1011   |      |           | add 3     |      |

| 1     | 0110   | 0010 |           | << #8     |      |

|       | 1<br>6 | 1    |           |           |      |

Goto wiki for more information and VHDL implementation

#### **Summary**

→More concurrent statements for DF modeling

→ describing routing structures

→ Modeling of basic combinational circuit blocks

→ Adders, multipliers, muxes, encoder/decoder

→ Generic design modeling

→ Using VHDL generics

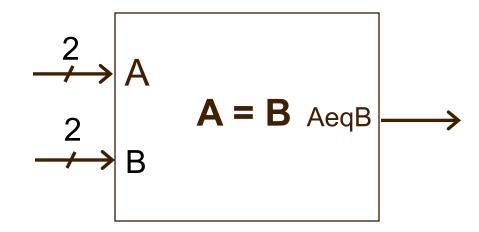

#### **Comparators**

#### **2-bit Number Comparator**

#### **4-bit Unsigned Number Comparator**

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all ;

entity compare is

port( A, B : in STD_LOGIC_VECTOR(1 downto 0);

AeqB : out

STD_LOGIC );

end compare ;

architecture dataflow of compare is

begin

AeqB <= '1' when A = B else

'0';

end dataflow :

```

#### **4-bit Unsigned Number Comparator**

```

library ieee;

use ieee.std_logic_1164.all;

entity compare is

port( A, B : in STD_LOGIC_VECTOR(1 downto 0);

AeqB : out STD_LOGIC );

end compare ;

-- Create a different model?

architecture dataflow of compare is

begin

```

#### **4-bit Signed Number Comparator**

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity compare is

port( A, B

: in STD_LOGIC_VECTOR(1 downto 0);

: out STD_LOGIC);

AeqB

end compare ;

architecture dataflow of compare is

begin

AeqB <= '1' when A = B else

'0':

```

end dataflow ;

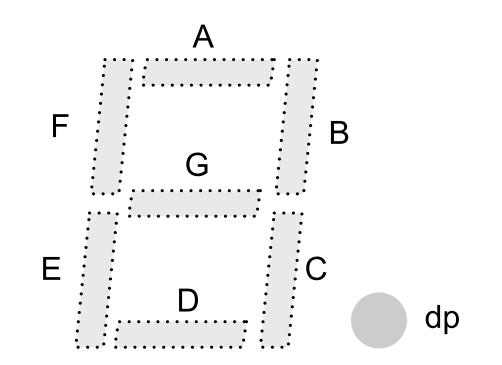

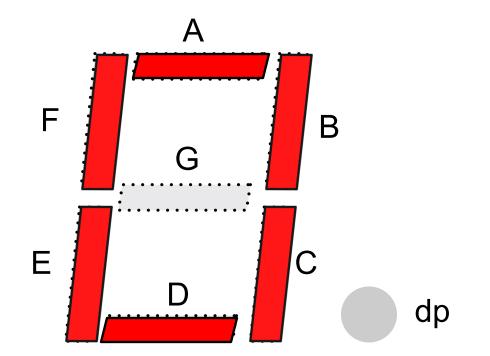

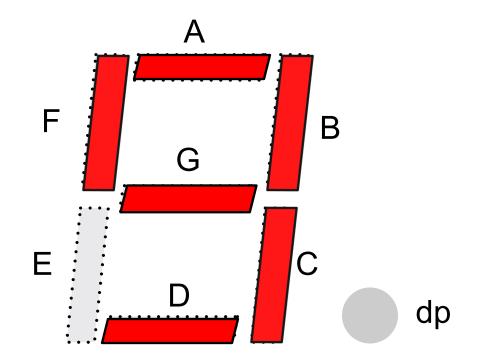

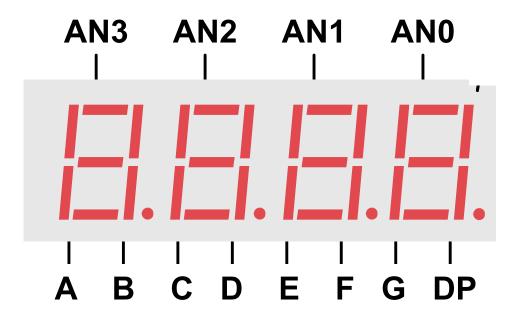

#### **Hexadecimal to 7-Segment Display**

To illuminate a segment, the corresponding control signal should be driven low.

To illuminate a segment, the corresponding control signal should be driven low -A = 0, 2, ..., F = 0, G = 1

To illuminate a segment, the corresponding control signal should be driven low -A = 0, 2, ..., E = 1, F = 0, G = 0

#### **Hex to 7-Segment**

| Hex Input | 7-Segment Control<br>GFEBCA |  |

|-----------|-----------------------------|--|

| 0000 (0)  | 100000                      |  |

| 0001 (1)  | 1111001                     |  |

| 0010 (2)  | 0100100                     |  |

| 0011 (3)  | 0110000                     |  |

| 0100 (4)  | 0011001                     |  |

| 0101 (5)  | 0010010                     |  |

| 0110 (6)  | 0000010                     |  |

| 0111 (7)  | 1111000                     |  |

| 1000 (8)  | 0000000                     |  |

| 1001 (9)  | 0010000                     |  |

| 1010 (A)  | 0001000                     |  |

- All four displays share common segment control signals.

- Only one display can be illuminated at a time when signal *ANx* is driven high.

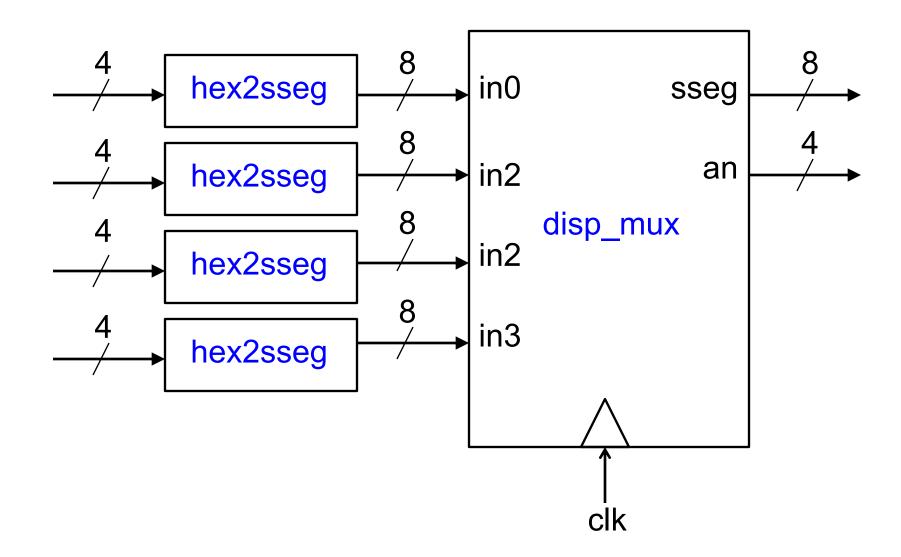

#### **7-Segment Display Controller**

#### **BCD to Binary Conversion**

- 1. Right shift bcd1, with the LSB shifting to the MSB of bcd0.

- 2. Right shift bcd0, with the LSB shifting to the MSB of bin.

- 3. If bcd0 is now > 4, subtract 3

- 4. repeat steps 1-3, 7 times.

# BCD to Binary Conversi

| <u>4 2</u> | → <u>0101010</u><br>42 |         |

|------------|------------------------|---------|

| Iteration: | BCD                    | bin     |

| 1          | 01000010               | 0000000 |

| >>         | 0100001                | 0000000 |

| 1≯4        |                        |         |

| 2          |                        |         |

| >>         | 010000                 | 1000000 |

| 0≯4        |                        |         |

| 3          |                        |         |

| >>         | 01000                  | 0100000 |

| 8 > 4, -3  | 00101                  | 0100000 |

| 4          | 0010                   | 1010000 |

| >>         | 0010                   | 1010000 |

| 2≯4        |                        |         |

| 5          | 001                    |         |

| >>         | 001                    | 0101000 |

| 1≯4        |                        |         |

| 6          |                        |         |

| >>         | 00                     | 1010100 |

| 0≯4        |                        |         |

| 7          |                        |         |

| >>         | 0                      | 0101010 |

| 0≯4        |                        |         |

binary

to

BCD

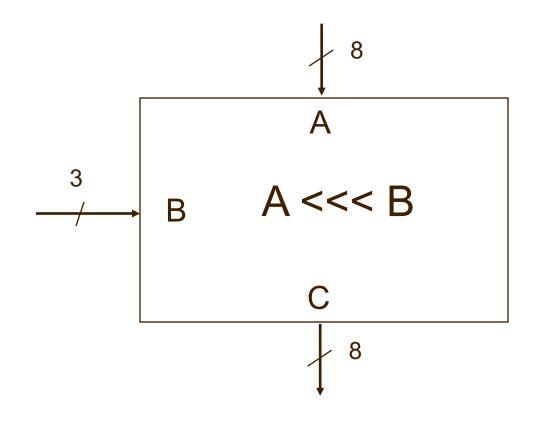

#### **8-bit Variable Rotator Left**

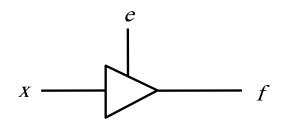

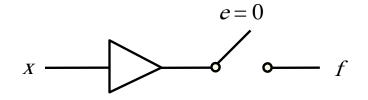

## **Tri-State Buffers**

#### **Tri-State Buffers**

(a) A tri-state buffer

| е | X | f |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Ζ |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

|   |   |   |

(b) Equivalent circuit

(c) Truth table

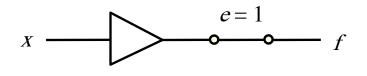

#### **Four types of Tri-state Buffers**

## **Tri-state Buffer – Example (1)**

LIBRARY ieee; USE ieee.std\_logic\_1164.all;

```

entity tri_state is

port( ena, input : IN STD_LOGIC;

output : OUT STD_LOGIC);

end tri_state;

```

architecture dataflow of tri\_state is begin

```

output <= input when (ena = '1') else

'Z';

```

end dataflow;

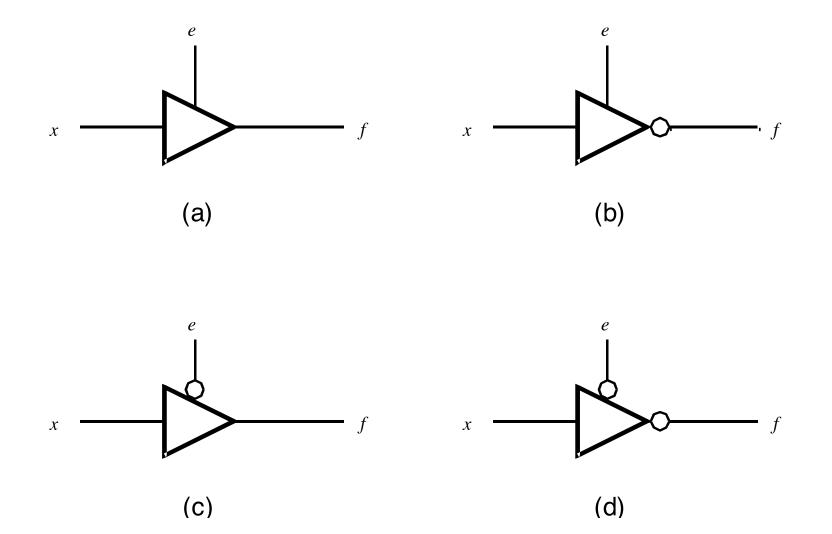

### **ROM 8x16 example (1)**

## ROM 8x16 example (2)

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

entity rom is

port ( Addr : in STD_LOGIC_VECTOR(2 downto 0);

Dout : out STD_LOGIC_VECTOR(15 downto 0));

end rom;

```

-- architecture body is defined on the next slide

## ROM 8x16 example (3)

```

architecture dataflow of rom is

signal temp: integer range 0 to 7;

type vector_array is array(0 to 7) of

std_logic_vector(15 downto 0);

constant memory : vector_array := ( X"800A",

x"D459",

X"A870",

x"7853",

x"650D",

x"642F",

X"F742",

X"F548");

begin

```

```

temp <= to_integer(unsigned(Addr));

Dout <= memory(temp);</pre>

```

end dataflow;